AEROSPACE REPORT NO. ATR-2023-01935

# Expanding Space Design Options Using COTS

September 6, 2023

Steven L. Hogan Digital & Integrated Circuit Electronics Department Electronics Engineering Subdivision

Prepared for: General Manager, Corporate Chief Engineer's Office

Authorized by: Corporate Chief Engineer's Office

For Public Release

## **MSIW Teams**

Two MSIW teams contributed to this report. Both provided significant contributions to this report.

#### **The Best Practices Team**

Dr. R. Rairigh (Lockheed Martin), Co-lead S. Hogan (Aerospace Corp), Co-lead R. DeLeon (Boeing) S. Duffy (Aerospace Corp) L. Harzstark (Aerospace Corp) J. Long (Raytheon) A. Para (Northrop Grumman) J. Ranaudo (Aerospace Corp) A. Sens (Boeing) Dr. B. Tabbert (Raytheon) A. Touw (Boeing) T. Wunderlich (Ball Aerospace)

#### The Workflow Team

M. Porter (NASA JPL), Co-lead S. Hogan (Aerospace Corp), Co-lead L. Harzstark (Aerospace Corp) Dr. J. Leitner (NASA GSFC) E. Minson (Maxar) A. Para (Northrop Grumman) J. Piacentine (Blue Canyon) Dr. R. Rairigh (Lockheed Martin) B. Tabbert (Raytheon) J. Walker (Maxar) T. Wunderlich (Ball Aerospace)

A big thanks to Brian Kosinski and Steve Lau for managing all the teams that contributed to this effort.

#### Abstract

The usage of Commercial Off the Shelf (COTS) components can provide impactful benefits to space programs. Space programs can benefit by accessing the latest performance technology and shorten procurement times for faster pace programs. This ATR (Aerospace Technical Report) provides guidance for determining the risk (cost, schedule, technical) of inserting COTS components or units on space vehicles as well as potential best practices and mitigations for many known COTS component or unit concerns.

| MS  | W Tear               | ns       |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|----------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abs | tract                |          |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.  | Execu<br>1.1         |          |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.  | Discu<br>2.1         |          |                                                                                                                                                                                                                                                                                                                  | lerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.  | Inform               | ned Risk | Flow                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.  | Best I<br>4.1<br>4.2 | Genera   | l COTS bes                                                                                                                                                                                                                                                                                                       | t Practices<br>es by Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.  | COTS<br>5.1          |          | Mitigation<br>Radiation<br>Useful Li<br>Manufact<br>Trust Que                                                                                                                                                                                                                                                    | Questions for Flow Section B<br>Questions<br>fe Questions<br>uring Questions<br>estions<br>nent Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 5.2                  |          | Mitigations<br>Radiation<br>5.2.1.1<br>5.2.1.1.1<br>5.2.1.1.2<br>5.2.1.1.3<br>5.2.1.1.4<br>5.2.1.1.5<br>5.2.1.2<br>5.2.1.2.1<br>5.2.1.2.1<br>5.2.1.2.2<br>5.2.1.2.3<br>5.2.1.2.4<br>5.2.1.2.5<br>5.2.1.3.1<br>5.2.1.3.1<br>5.2.1.3.2<br>5.2.1.3.3<br>5.2.1.3.4<br>5.2.1.4.1<br>5.2.1.4.2<br>5.2.1.4.3<br>5.2.1.5 | for Flow Section E<br>Total Dose<br>Local Shielding (1a)<br>Power Strobing (1b)<br>Increased Redundancy (1c)<br>N for M Redundancy (1d)<br>Multiple Images (1e)<br>Multiple Components in Parallel (1f)<br>Single Event Upsets<br>Periodic Refresh (1g)<br>Error Detection and Correction (1h)<br>Triple Modular Redundancy (1j)<br>FPGA-based Scrubbing (1k)<br>Zener Diodes Clamps and Filters (11)<br>Software Rollback (1m)<br>Single Event Functional Interrupt<br>Local Refresh (1n)<br>Component Reset (1o)<br>Power Cycle (1p)<br>CURTENT Limiting (1r)<br>Swap or Power Cycle by Fault Protection (1s)<br>Auto Power Cycle by the Hardware (1t)<br>Single Event Gate Rupture | $\begin{array}{c} & 40 \\ & 41 \\ & 43 \\ & 43 \\ & 43 \\ & 43 \\ & 43 \\ & 43 \\ & 43 \\ & 43 \\ & 44 \\ & 44 \\ & 44 \\ & 44 \\ & 44 \\ & 44 \\ & 44 \\ & 44 \\ & 44 \\ & 44 \\ & 44 \\ & 44 \\ & 44 \\ & 44 \\ & 44 \\ & 44 \\ & 45 \\ & 45 \\ & 45 \\ & 45 \\ & 45 \\ & 45 \\ & 45 \\ & 45 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 46 \\ & 47 \\ \end{array}$ |

|     |                      | 5.2.2    | 5.2.1.5.1<br>Useful Li<br>5.2.2.1                                                                                                                                                                                                                                                                                | Conservative Derating (1u)<br>fe<br>High Temperature Operational Life Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## Contents

|           | 5.2.2.1.1  | Accelerated Life Test for Temperature (2a)                  |    |    |

|-----------|------------|-------------------------------------------------------------|----|----|

|           | 5.2.2.2    | High Temperature Operational Life Voltage                   | 49 |    |

|           | 5.2.2.2.1  | 5.2.2.2.1 Life Test at Usage Voltage (2b)                   | 49 |    |

|           | 5.2.2.3    | High Temperature Operational Life Frequency                 | 49 |    |

|           | 5.2.2.3.1  | Life test at Usage Frequency (2c)                           |    |    |

|           | 5.2.2.4    | No HTOL or Reliability Data                                 |    |    |

|           | 5.2.2.4.1  | Extensive Accelerated Testing, EM or Unit Testing (2d)      |    |    |

|           | 5.2.2.4.2  | Focused Accelerated testing of the COTS Component (2e)      |    |    |

|           | 5.2.2.4.3  | Focused Testing of Like Process Structures (2f)             |    |    |

|           | 5.2.2.4.4  | Effects on System Reliability (2g)                          |    |    |

| 5.2.3     |            | y ()                                                        |    | 50 |

| - · · · - | 5.2.3.1    | Plastic Package                                             |    |    |

|           | 5.2.3.1.1  | Plastic Package encapsulation (3a)                          |    |    |

|           | 5.2.3.1.2  | Package Hermeticity (3b)                                    |    |    |

|           | 5.2.3.1.3  | Repackage Component (3c)                                    |    |    |

|           | 5.2.3.2    | Reworkability                                               |    |    |

|           | 5.2.3.2.1  | Risk Reduction Activity (3d)                                |    |    |

|           | 5.2.3.2.2  | Daughtercard Implementation (3e)                            |    |    |

|           | 5.2.3.2.3  | Easy to Replace Design (3f)                                 |    |    |

|           | 5.2.3.3    | Electrical Testing                                          |    |    |

|           | 5.2.3.3.1  | Enhanced Component Testing (3g)                             |    |    |

|           | 5.2.3.3.2  | Early Risk Reduction Circuit (3h)                           |    |    |

|           | 5.2.3.3.2  | Board Level Test (3j)                                       |    |    |

|           | 5.2.3.3.4  | Unit Level Test (3)                                         |    |    |

|           | 5.2.3.3.4  |                                                             |    |    |

|           | 5.2.3.4    | Lack of Component Level Burn-in Data (31)<br>Pure Tin Leads |    |    |

|           |            |                                                             |    |    |

|           | 5.2.3.4.1  | Double Layer of Conformal Coat (3m)                         |    |    |

|           | 5.2.3.4.2  | Re-Tin Leads or Repackage (3n)                              |    |    |

|           | 5.2.3.4.3  | Solder Wicking (30)                                         |    |    |

|           | 5.2.3.4.4  | Fusing (3p)                                                 |    |    |

|           | 5.2.3.4.5  | Annealing (3q)                                              |    |    |

|           | 5.2.3.4.6  | Matte Tin Plating (3r)                                      |    |    |

|           | 5.2.3.5    | Package RGA                                                 |    |    |

|           | 5.2.3.5.1  | Test the Component (3s)                                     |    |    |

|           | 5.2.3.6    | Particle Impact Noise Detection                             |    |    |

|           | 5.2.3.6.1  | Test the Component (3t)                                     |    |    |

|           | 5.2.3.7    | Bondpull                                                    |    |    |

|           | 5.2.3.7.1  | Bondpull Test the Component (3u)                            |    |    |

|           | 5.2.3.8    | Shock.                                                      |    |    |

|           | 5.2.3.8.1  | Shock Test the Component (3v)                               |    |    |

|           | 5.2.3.9    | Vibration                                                   |    |    |

|           | 5.2.3.9.1  | Vibration Test the Component (3w)                           |    |    |

|           | 5.2.3.10   | Burn-in                                                     |    |    |

|           | 5.2.3.11   | Lot Travelers                                               |    |    |

|           | 5.2.3.11.1 | On-Site Inspection (3y)                                     | 63 |    |

|           |            | Early Non-Destructive and Destructive Tests (3z)            |    |    |

|           | 5.2.3.12   | Electro-Static Discharge                                    |    |    |

|           |            | ESD Sensitivity Testing (3aa)                               |    |    |

|           | 5.2.3.13   | Barometric Pressure                                         |    |    |

|           |            | Pressure Test the Component (3ab)                           |    |    |

|           | 5.2.3.14   | Solderability                                               | 65 |    |

|       | 5.2.3.14.1 | Test the Component for Solderability(3ac)                        |       |

|-------|------------|------------------------------------------------------------------|-------|

|       | 5.2.3.15   | Lid Seal                                                         |       |

|       | 5.2.3.15.1 | Test the Component for Lid Seal(3ad)                             | 65    |

|       | 5.2.3.16   | Radiography                                                      |       |

|       | 5.2.3.16.1 | Radiographically Test the Component (3ae)                        | 65    |

|       | 5.2.3.17   | Resistance to Solvents                                           | 67    |

|       | 5.2.3.17.1 | Test the Component for Resistance to Solvents(3af)               | 67    |

|       | 5.2.3.18   | Scanning Acoustic Microscopy                                     |       |

|       | 5.2.3.18.1 | SAM Test the Component (3ag)                                     |       |

|       | 5.2.3.19   | Moisture                                                         |       |

|       |            | Moisture Test the Component (3ah)                                |       |

|       | 5.2.3.20   |                                                                  |       |

|       |            | Test the Component for Lead Finish (3aj)                         |       |

|       | 5.2.3.20.1 | Die Shear                                                        |       |

|       |            | Die Shear Test the Component (3ak)                               |       |

|       | 5.2.3.22   | Lid Torque                                                       |       |

|       |            | Lid Torque Test the Component (3al)                              |       |

|       | 5.2.3.23   | Lead Adhesion                                                    |       |

|       |            | Test the Component for Lead Adhesion(3am)                        |       |

|       | 5.2.3.24   | Column Pull                                                      |       |

|       |            |                                                                  |       |

|       |            | Pull Test the Component (3an)                                    |       |

|       | 5.2.3.25   | External Visual                                                  |       |

|       |            | On-Site Inspection or Observation (3ao)                          |       |

|       |            | External Visual post Component Receipt (3ap)                     |       |

|       | 5.2.3.26   | Pre-Cap Inspection                                               |       |

|       |            | On-Site Inspection or Observation (3aq)                          |       |

|       | 5.2.3.27   | Internal Visual                                                  |       |

|       |            | On-Site Inspection or Observation (3ar)                          |       |

|       |            | De-Lid and Inspect Component (3as)                               |       |

|       | 5.2.3.28   | Scanning Electron Microscopy                                     |       |

|       |            | SEM Test the Component (3at)                                     |       |

|       | 5.2.3.29   | Contamination                                                    |       |

|       |            | Existing Mitigations (3au)                                       |       |

|       | 5.2.3.30   | Hazardous materials                                              |       |

|       |            | Existing Mitigations (3av)                                       |       |

|       |            | Handling (aw)                                                    | 75    |

|       | 5.2.3.31   | Corrosive Materials                                              |       |

|       |            | Separation of Functions/Containment (3ax)                        |       |

| 5.2.4 |            |                                                                  |       |

|       | 5.2.4.1    | Foreign Sourced                                                  |       |

|       | 5.2.4.1.1  | Review of component (4a)                                         |       |

|       | 5.2.4.1.2  | Alternate Design (4b)                                            |       |

|       | 5.2.4.1.3  | Limit Usage in System Design (4c)                                | 78    |

|       | 5.2.4.1.4  | Blind Trusted Agent Buy (4d)                                     | 78    |

|       | 5.2.4.1.5  | Independent Verification and Validation for Critical Functions ( | 4e)78 |

|       | 5.2.4.2    | Heritage                                                         |       |

|       | 5.2.4.2.1  | Counterfeit Components (4f)                                      | 78    |

| 5.2.5 | Environm   | ental Considerations                                             |       |

|       | 5.2.5.1    | Aging                                                            |       |

|       | 5.2.5.1.1  | Multiple Components in Parallel (5a)                             |       |

|       | 5.2.5.1.2  | Conservative De-rating (5b)                                      |       |

|       |            | -                                                                |       |

|    |      | 5.2.5.1.3      | Conservative Thermal Environment (5c)     |    |

|----|------|----------------|-------------------------------------------|----|

|    |      | 5.2.5.1.4      | Dynamic Reliability Management (5d)       |    |

|    |      | 5.2.5.1.5      | Adaptive/Static Voltage Scaling (5e)      |    |

|    |      | 5.2.5.2        | Temperature                               |    |

|    |      | 5.2.5.2.1      | Local Heatpipes (5f)                      |    |

|    |      | 5.2.5.2.2      | Lower Supply Voltages (5g)                |    |

|    |      | 5.2.5.2.3      | Decreased Frequency (5h)                  |    |

|    |      | 5.2.5.3        | Vacuum                                    |    |

|    |      | 5.2.5.3.1      | Conservative Derating (5j)                |    |

|    |      | 5.2.5.3.2      | Increased Physical Spacing (5k)           |    |

|    |      | 5.2.5.3.3      | No "Golden" Nodes (51)                    |    |

|    |      | 5.2.5.3.4      | Encapsulation (5m)                        |    |

|    |      | 5.2.5.3.5      | Deployable Covers for Optics (5n)         |    |

|    |      | 5.2.5.3.6      | Unit Thermal Vacuum Test (50)             |    |

|    |      | 5.2.5.4        | EMC/EMI                                   |    |

|    |      | 5.2.5.4.1      | Shielding (5p)                            |    |

|    |      | 5.2.5.4.2      | Grounding (5q)                            |    |

|    |      | 5.2.5.4.3      | Power Strobing - Filtering (5r)           | 83 |

| 6. | Flow | Usage Examples |                                           | 84 |

| 0. | 6.1  | COTS Example 1 | On Board Computer Controller (OBCC) ~1988 |    |

|    | 6.2  | <b>1</b>       | Various programs – EEPROM usage ~2003     |    |

|    | 6.3  |                | Computer and Data Electronics (CDE)       |    |

| _  |      | •              | •                                         |    |

| 7. |      |                |                                           |    |

| 8. | Acro | nyms           |                                           |    |

|    |      |                |                                           |    |

## Figures

| Figure 1.  | Informed risk flow (A to E).                                 |    |

|------------|--------------------------------------------------------------|----|

| Figure 2.  | Informed risk flow – Determine COTS risk tolerance (A to B). |    |

| Figure 3.  | Informed risk flow – COTS mitigation scope (B to C)          |    |

| Figure 4.  | Informed risk flow – Scoping risk mitigation (C to D)        |    |

| Figure 5.  | Informed risk flow – Selecting the design solution (D to E). |    |

| Figure 6.  | Component selection, identification and mitigation flow      |    |

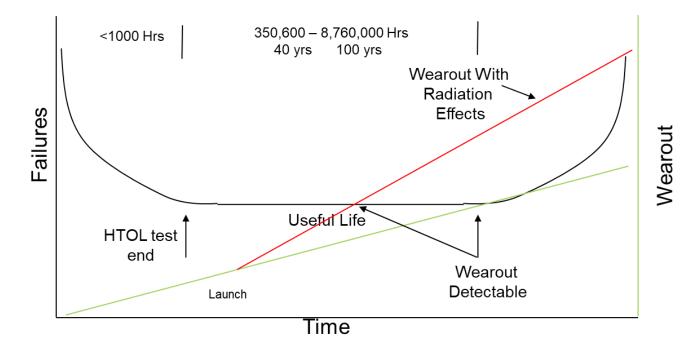

| Figure 7.  | Useful life with radiation.                                  |    |

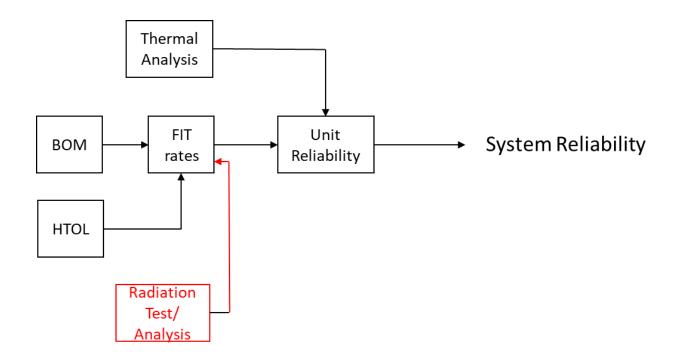

| Figure 8.  | Useful life FIT rate including radiation.                    |    |

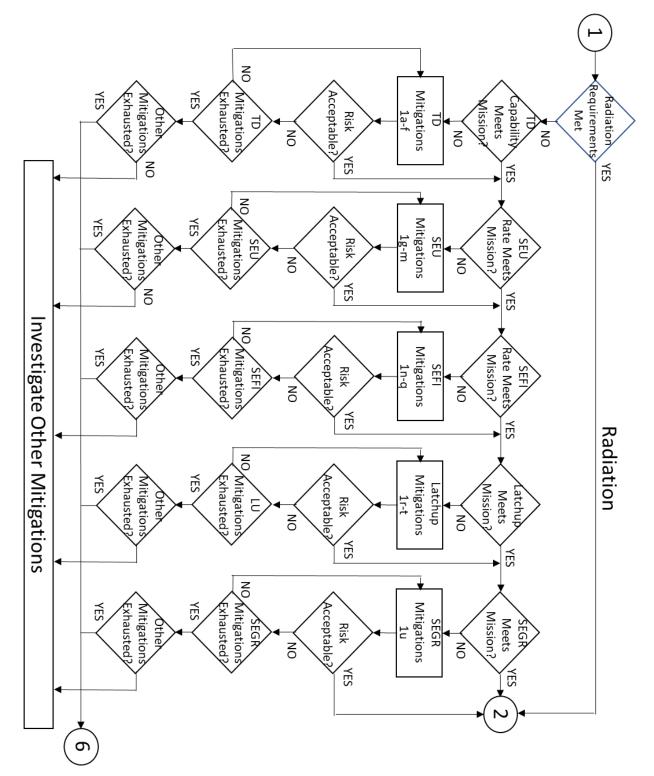

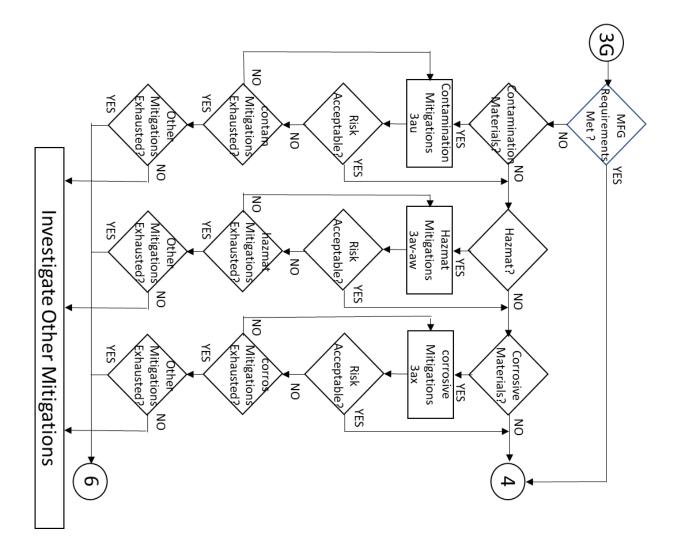

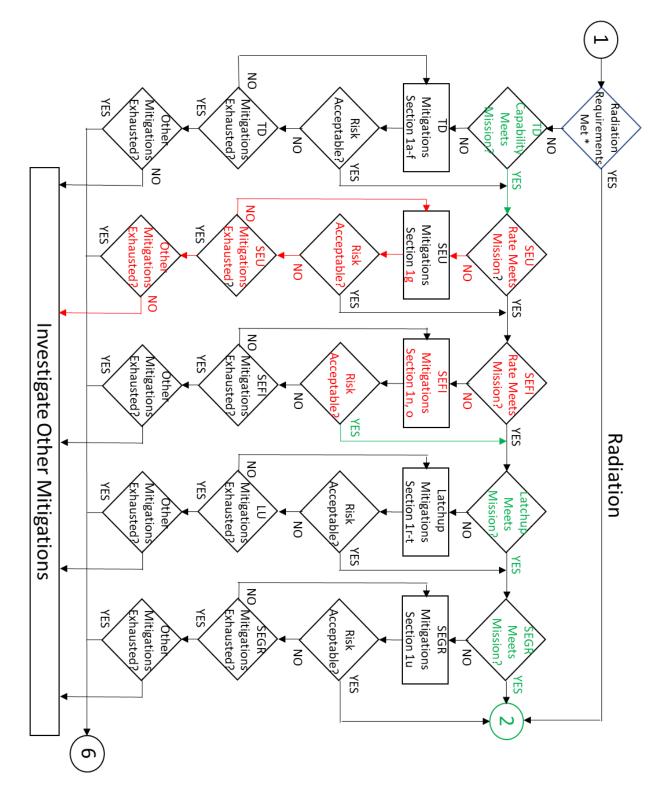

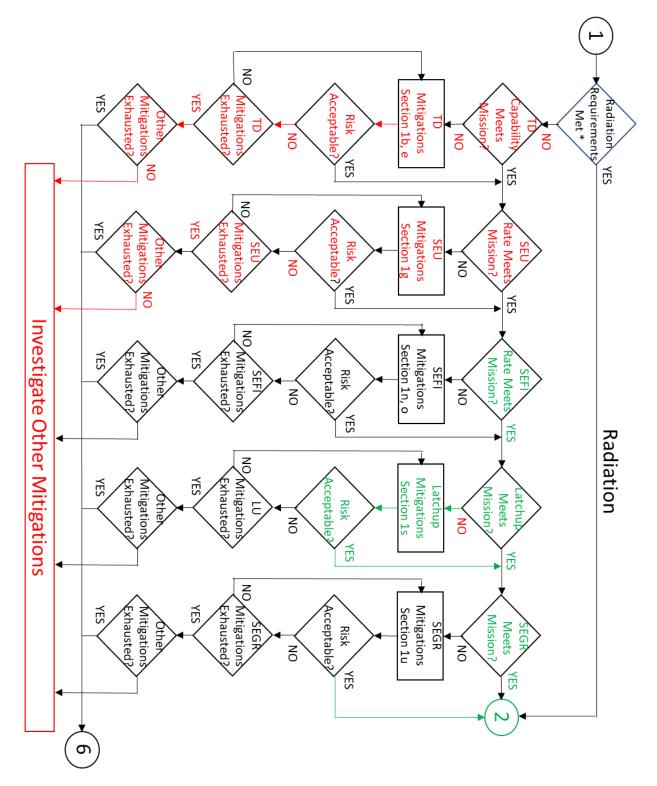

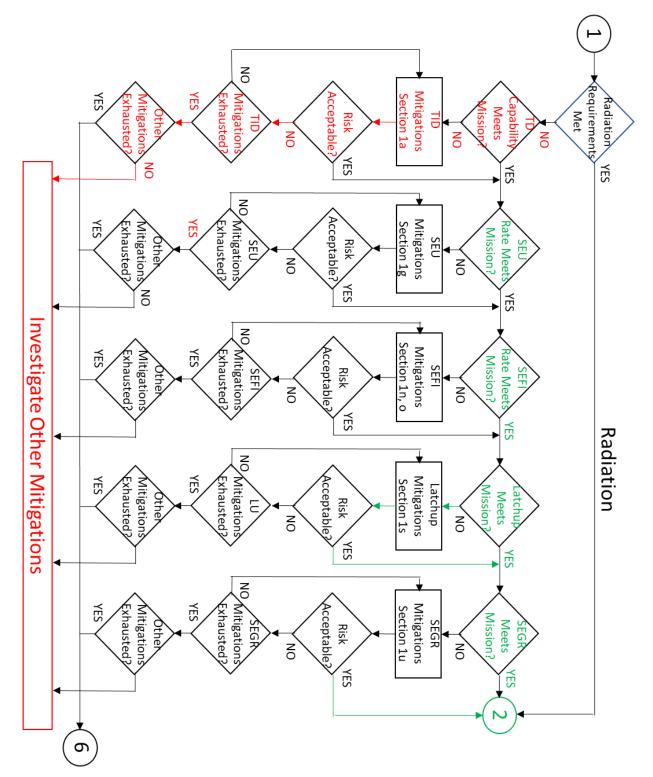

| Figure 9.  | Radiation mitigations flow                                   |    |

| Figure 10. | Useful life mitigations flow.                                |    |

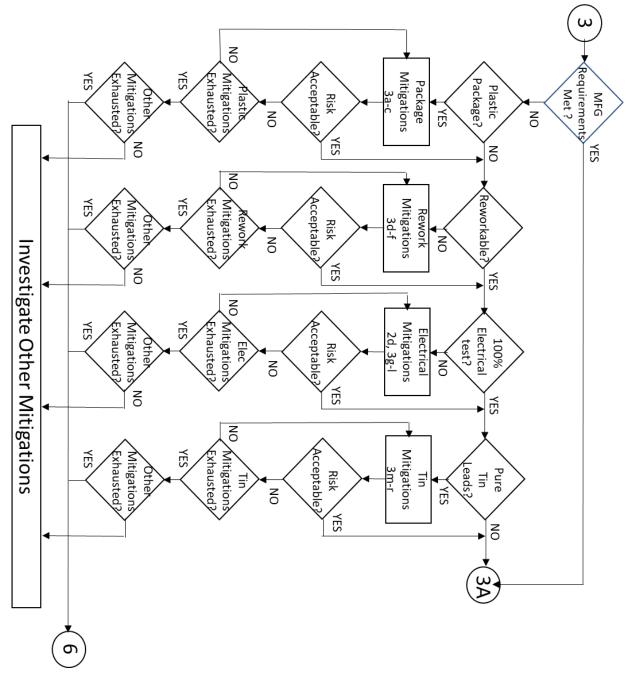

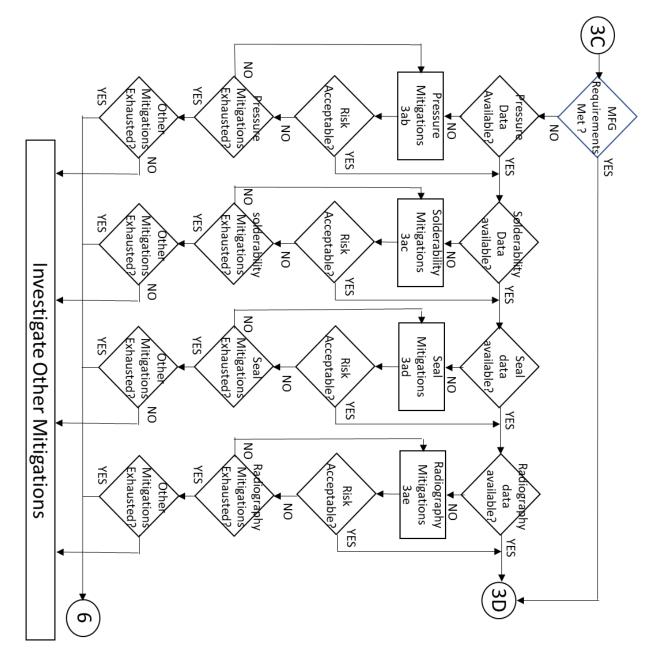

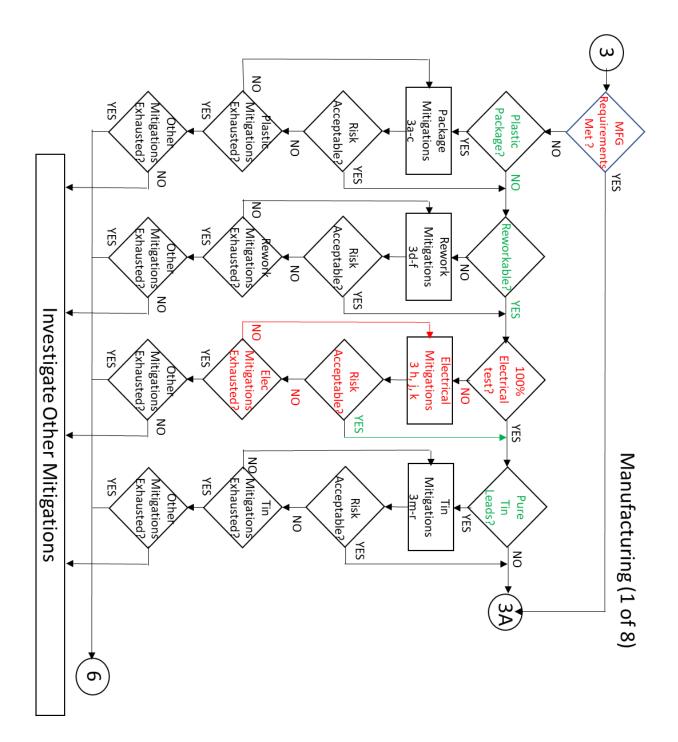

| Figure 11. | Manufacturing mitigation flow (1 of 8).                      | 53 |

| Figure 12. | Manufacturing mitigation flow (2 of 8).                      |    |

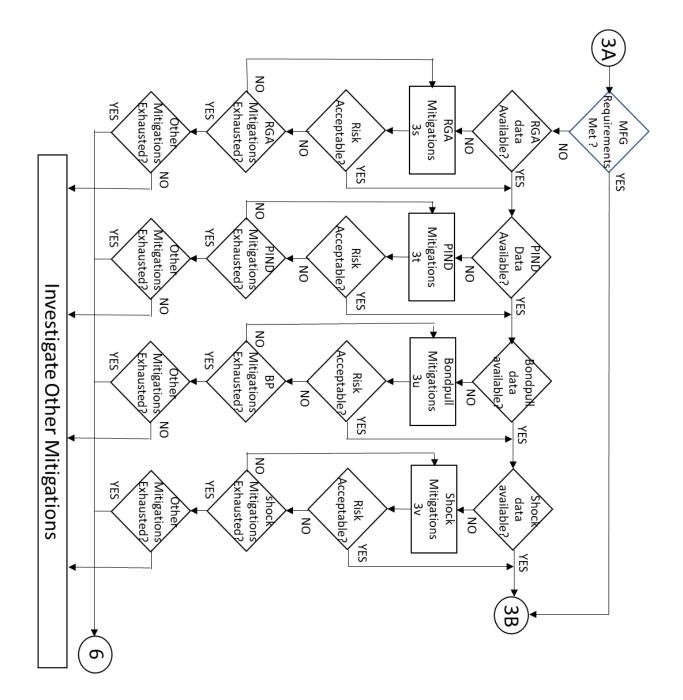

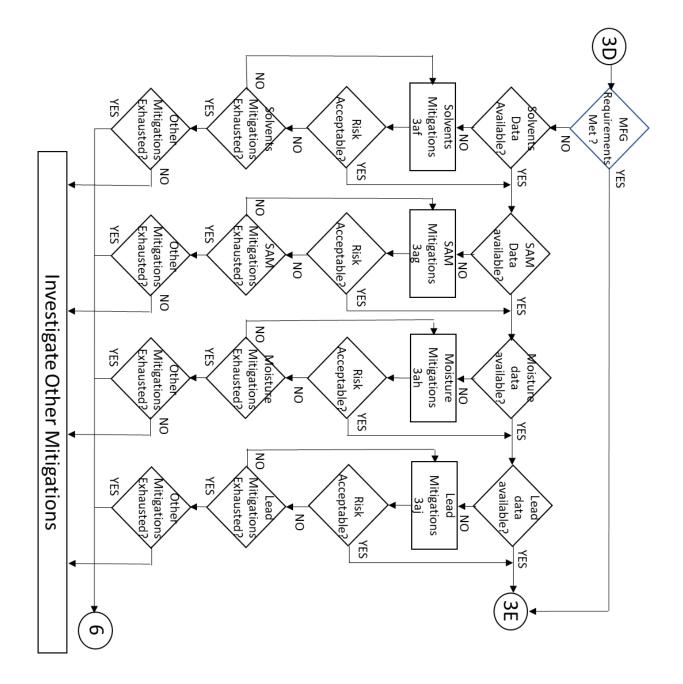

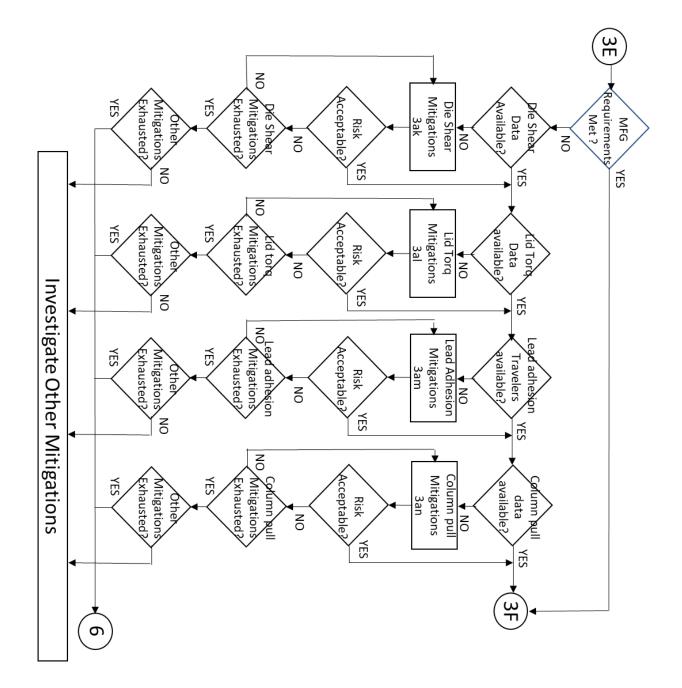

| Figure 13. | Manufacturing mitigation flow (3 of 8).                      | 61 |

| Figure 14. | Manufacturing mitigation flow (4 of 8).                      | 64 |

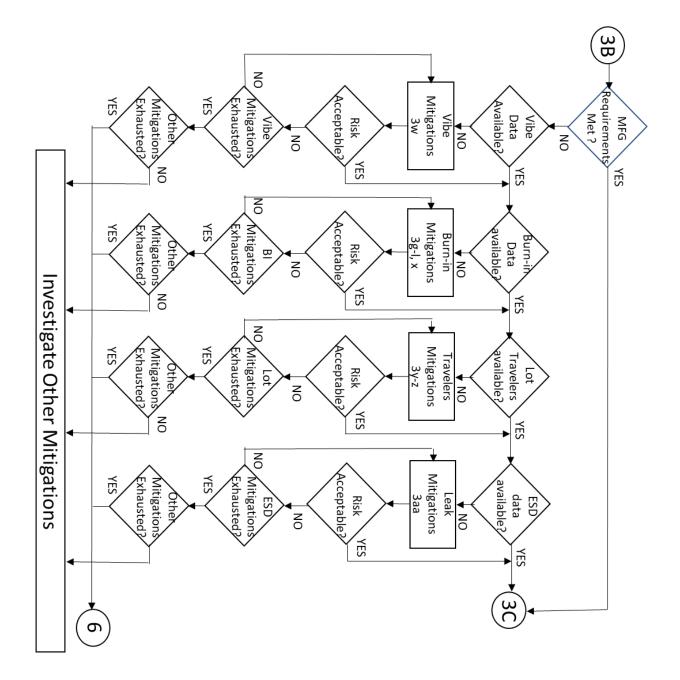

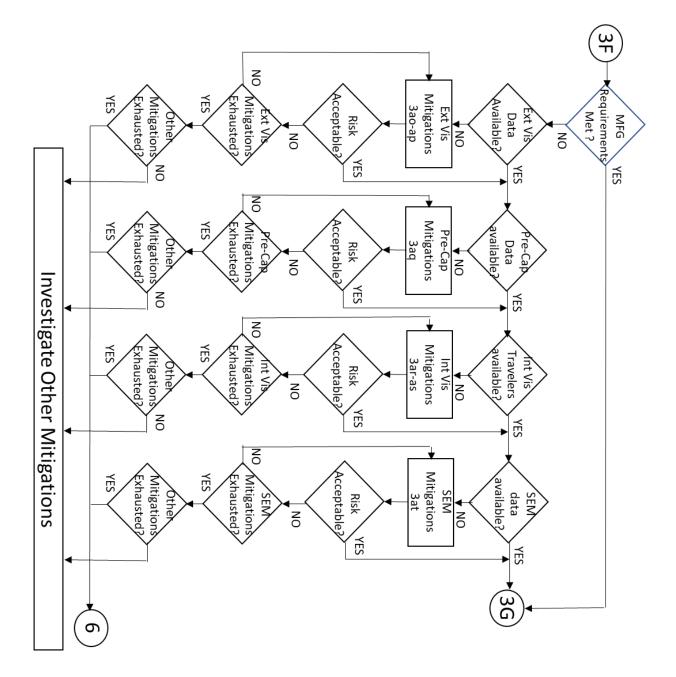

| Figure 15. | Manufacturing mitigation flow (5 of 8).                      |    |

| Figure 16. | Manufacturing mitigation flow (6 of 8).                      | 69 |

| Figure 17. | Manufacturing mitigation flow (7 of 8).                      |    |

| Figure 18. | Manufacturing mitigation flow (8 of 8).                      | 74 |

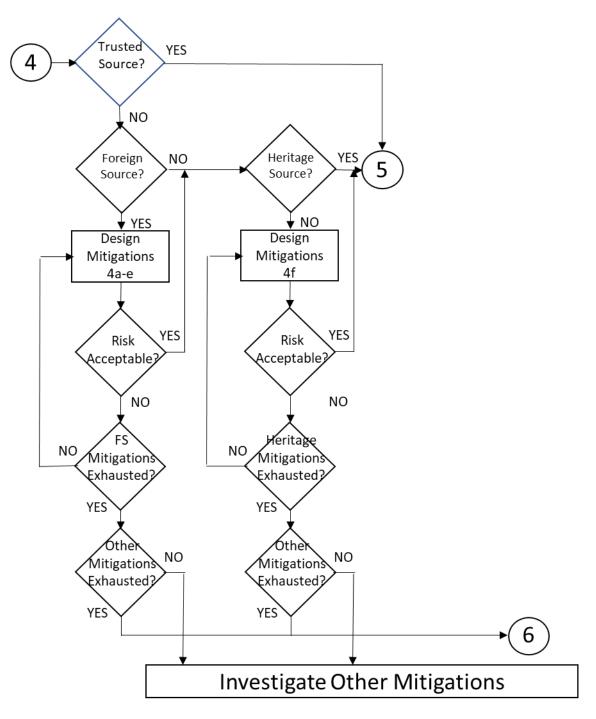

| Figure 19. | Trust mitigations flow                                       |    |

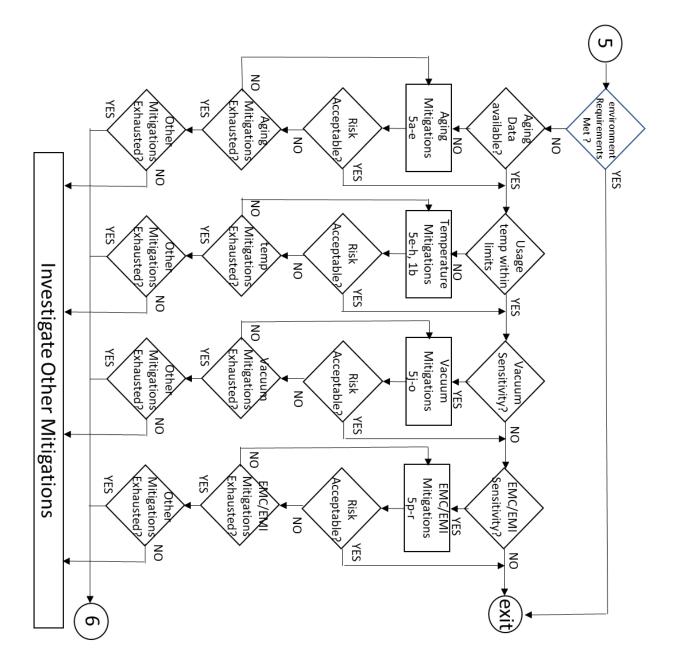

| Figure 20. | Environmental mitigations flow.                              | 80 |

| Figure 21. | OBCC processor SEU mitigation example                        | 85 |

| Figure 22. | EEPROM mitigation example.                                   |    |

| Figure 23. | Example 3 flow example (1 of 2).                             |    |

| Figure 24. | Example 3 flow example (2 of 2).                             |    |

## Tables

| Table 1.  | Supplier Best Practices                                    | 16 |

|-----------|------------------------------------------------------------|----|

| Table 2.  | General Best Practices for the Component User              | 17 |

| Table 2.  | General Best Practices for the Component User (cont)       | 18 |

| Table 2.  | General Best Practices for the Component User (cont)       | 19 |

| Table 2.  | General Best Practices for the Component User (cont)       | 20 |

| Table 3.  | COTS Resistor User Best Practices                          | 21 |

| Table 4.  | COTS Capacitor User Best Practices                         | 21 |

| Table 5.  | COTS Connector User Best Practices                         | 22 |

| Table 6.  | COTS Diode User Best Practices                             | 22 |

| Table 7.  | COTS Inductor User Best Practices                          | 22 |

| Table 8.  | COTS Bipolar Junction Transistor (BJT) User Best Practices | 22 |

| Table 9.  | COTS Field Effect Transistor (FET) User Best Practices     | 23 |

| Table 10. | COTS Power Transistor User Best Practices                  | 23 |

| Table 11. | COTS Radio Frequency (RF) Transistor User Best Practices   | 23 |

| Table 12. | COTS OP-Amp/Comparator User Best Practices                 |    |

| Table 13. | COTS Pulse Width Modulators User Best Practices            | 23 |

| Table 14. | COTS Relay User Best Practices                             | 24 |

| Table 15. | COTS Printed Wiring Board User Best Practices              | 24 |

| Table 16. | COTS Fuse User Best Practices                              | 24 |

| Table 17. | COTS Wire User Best Practices                              | 24 |

| Table 18. | COTS Integrated Circuit/Hybrid User Best Practices         | 25 |

| Table 18. | COTS Integrated Circuit/Hybrid User Best Practices (cont)  |    |

| Table 19. | LM139A SMD Comparison                                      | 27 |

| Table 20. | Potential Radiation Mitigations                            | 41 |

| Table 21. | Potential Useful Life Mitigations                          | 47 |

| Table 22. | Potential Manufacturing Mitigations                        | 51 |

| Table 22. | Potential Manufacturing Mitigations (cont)                 | 52 |

| Table 23. | Potential Trust Mitigations                                | 76 |

| Table 24. | Potential Environmental Considerations Mitigations         | 79 |

## 1. Executive Summary

The space industry is being challenged by a heightened focus on their customer's desire/mandate to dramatically shorten the time from contract award to launch and the need for using the leadingedge/cutting-edge technology offered by commercially available electronic components.<sup>1</sup> This juncture marks a conscious decision to reduce one's traditional reliance of military component offerings and to implement the use of Alternate Grade Parts (AGP) also known as Commercial Off The Shelf (COTS) components that better align with these current program's technical and schedule restraints. In this ATR, COTS is defined as "A cataloged Electric, Electronic, and Electromechanical (EEE) component for which the US Government or its contractors does not control the specification. The item manufacturer, or non-government bodies (such as the Automotive Electronics Council), solely establishes and controls the specifications for performance, configuration, and reliability (including design, materials, processes, and testing) without additional requirements imposed by users". This ATR provides a sound, prudent, and time proven approach for leveraging the benefits of COTS components, while ensuring that the EEE COTS components chosen will satisfy all contract and mission parameters.

This paper provides a holistic approach that does not focus solely on the EEE components needed to build the hardware. The contract language, mission category, risk tolerance, and design mitigations (at the unit, system, and constellation levels) are integral parts that contribute to the determination of the EEE components chosen. It is imperative for the team members within the management, contract, design, and component selection organizations to agree upon the acceptable risk level for the mission category at hand. Once these factors have been made known and incorporated into the program's design and performance baseline, the components selection organization will be able to determine the quality and reliability level for the needed EEE components.

This ATR provides a series of questions whose answers will determine the ability of the EEE components chosen to satisfy all mission requirements. These questions have evolved from those asked when space flight first became a reality in the 1960s and house the knowledge the industry has learned from its mistakes. These questions need to be asked and answered regardless of the genre of components used (Mil-Spec or Commercial Off the Shelf) or the category of mission at stake (Class A, B, C or D). The answers will vary according to the mission category and risk profile acceptable for a given contract. To illustrate this point, the EEE components chosen for a Class A mission will have more stringent component history, qualification, and build knowledge requirements than those for a Class D mission. It is incumbent for the components selection organization to determine if the available data is sufficient to make an informed risk decision as to the component's ability to satisfy all contractual and mission requirements or if additional mitigations are necessary to bridge the gaps needed to make that decision.

To achieve the performance, cost, and schedule goals of these new proliferated space systems, the systems will need to be architected with more than Mil-Spec components in mind and may require use of COTS buses, systems, and components. This ATR provides guidance for increasing the trade space of possible solutions with regards to availability in contested space (informed risk of using COTS in space) with a holistic, reliable, and repeatable approach.

#### 1.1 Overview

The focus and products of this ATR is to enable the United States Government (USG) and its contractors to adapt to a changing landscape where the traditional approach to component selection, unit design and test, and system design and test will not meet performance, cost or schedule needs to achieve the mission.<sup>1</sup> Specifically, it lays out a framework that addresses this changing landscape by providing guidance on how EEE COTS components may be inserted in the technical baseline with a risk-informed

approach to directly address mission needs. This ATR is taking the NEXT STEP after the recent work performed by the NASA Engineering and Safety Council (NESC) on recommendations for COTS use in NASA missions which introduces the terminology of Industry Leading Part Manufacturers (ILPM) from established manufacturers that are already producing high quality, high volume, state-of-the-art, feature rich COTS components, and established COTS.<sup>2</sup> The methodology outlined in this ATR is relevant to all missions and mission classes.

Traditional component selection approaches to inserting COTS into a design focus on taking the asdesigned /as-built component from the supplier and subjecting it to tests and screens (up-screening) that attempt to demonstrate the component is compliant to the relevant requirements in an existing components assurance or control document (e.g. TOR-2006(8583)-5236, EEE-INST-002). Generally, these controls define a standard baseline that specifies usage of military specification components (MIL-PRF-38535 for microcircuits, MIL-STD-19500 for Semiconductors, and MIL-PRF-123 for ceramic capacitors to name a few examples) and the relevant test requirements from those specifications to demonstrate the compliance of the component to the pertinent set of quality requirements. This traditional approach presents risks in the context of the changing landscape for the following reasons:

- a) Up-screening introduces significant schedule considerations (> 24 52 weeks) [Schedule Risk]

- b) Mil-Spec Up-screening subjects COTS components to test levels that they may not have been designed to meet and are not directly derived from the relevant design application resulting in risk of component failure by exceeding the data sheet limits – [Cost or Schedule Risk (potential failure in ground testing) and Technical Risk (potential failure or performance degradation onorbit)]

- c) Historically, these risks would not have been recognized (captured in a program risk register) as they are part of the technical baseline under the traditional approach. However, under the changing landscape, particularly the reduced time between Authorization to Proceed (ATP) and launch, they must be recognized as risks in the context of executing the mission. This is because the component-level hardware risks can lead to impacts to unit or system-level assembly and test aimed at verification of mission requirements. This, in turn, can introduce programmatic risk (delays to capability or mission availability) or technical risk from escapes due to an accelerated or abbreviated system verification campaign that results in failure or performance degradation onorbit.

An overarching theme of the changing landscape is the need to establish an informed mission risk profile that addresses the acceptable risk of failure for given conditions. Failure, in this context includes the traditional notions of hardware failure in operations, but also failure to achieve the required mission availability due to schedule delay. The ability to select components (not just COTS) for the mission will directly result from this informed mission risk profile.

This ATR is broken into six sections and is designed for use by multiple organizations responsible for mission execution:

- a) Section 1 (Executive Summary), Section 2 (Discussion), and Section 3 (Informed Risk) are intended for USG and contractor program management and systems engineering for setting the stage and guidance to determine the informed risk and provide background for the best practices and mitigations.

- b) Section 4 (Best Practices) and Section 5 (Mitigations) are intended for systems engineering, design engineering, radiation/survivability engineering, components engineering and materials and process engineering organizations to determine the impact of using COTS in the application

with many suggestions for system mitigations that don't require the traditional approaches, such as expensive and time-consuming component up-screening.<sup>2</sup>

c) Section 6 (Flow Usage Examples) provides examples on using the mitigation flows.

There are several major points that are manifest across the document and summarized, as follows:

- a) Most potential component-level risks are addressed by selecting a COTS supplier that implements the prescribed best practices in Section 4. Component selection is the key, working within the chosen component's datasheet limits. Most of Section 5 content is provided for when no component can meet the conditions in the relevant application.

- b) Applying risk mitigation in Section 5, stemming from uncertainty in a supplier's component assurance or limitations in component design, testing, or application should occur across design elements and lifecycle in a manner that optimizes cost, technical, and schedule impacts for the mission and should not be restricted to the component level. Examples:

- Implement board-level test programs to address risk from lack of burn-in or 100% electrical test in a COTS component.

- Using a robust tin whisker mitigation manufacturing program (lead-solder reflow in circuit card assembly manufacturing, applying conformal coating) to address risk from lead-free components.

- c) Automotive Electronic Council (AEC) passive (AEC-Q200) and discrete (AEC-Q101) components procured from suppliers that share Level 3 Production Part Approval Process (PPAP) data (Best Practice by supplier) represent a low-risk COTS solution for most missions when used within their datasheet parameters and with appropriate derating for the application.

- d) Complex components (field programmable gate arrays (FPGA), System on a Chip (SoC), multicore processors, etc.) are a major focus for best practices in Section 4 and risk mitigation in Section 5 because they largely represent the performance enablers required to meet mission needs under the changing landscape.

The solutions are not component centric, but are holistic, combining component best practices with board, unit, and system mitigations to arrive at a total solution. This holistic approach includes recommendations on how the contract needs to be structured to embrace this new approach. These recommendations are identified in Acquisition Considerations to Expand Space Design Options using COTS Electrical, Electronic, and Mechanical (EEE) Parts and Units (ATR-2023-01981). This expanding space design options ATR is organized to provide a general overview of the usage of COTS for space, followed by a discussion and then a suggested flow for determining the component risk associated with a component that does not have sufficient basis for reliability in the application, followed by supplier and user best practices, both general and component specific. Following the best practices section, the mitigations section contains detailed risk assessment questions and associated component risk mitigations. The mitigations section also includes several examples of usage of non Mil-Spec components before Mil-Spec components existed to meet a specific need and how they were used successfully. When the design solution does not include components that fully meet component assurance need for the mission then other best practices and mitigations may be employed to sufficiently lower the mission risk. These are covered in Section 4 and 5. Section 6 provides the same non Mil-Spec examples using the flow charts from Section 5 to guide the reader on how to use the Section 5 flow to determine the necessary mitigations for the chosen component.

Besides the value of using COTS components for quick-turnaround, short duration missions where components with unknown life performance are acceptable, there are COTS components that can benefit

any class of mission. Complex components with significant leverage are Systems On a Chip (SOC), multicore processors, Application Specific Integrated Circuits (ASICs), Field Programmable Gate Arrays (FPGA), memory (SDRAM, FLASH), Standard Interfaces (i.e. Ethernet), Charge Coupled Devices (CCD) Analog to Digital Converters (ADC) and high speed and precision amplifiers. Components used in large quantities, both active and discrete, such as interface components, amplifiers, resistors, capacitors, transistors, and diodes are also good candidates for COTS space usage.

## 2. Discussion

EEE component assurance for space hardware has historically been focused on ensuring the quality of each lot of components through a series of screening and qualification tests, such as radiation hardness, including single event effects (SEEs), accelerated life testing, shock and vibration, temperature cycling and more. Ensuring component quality through these lot specific tests has been the standard method to eliminate infant mortality and to claim long term component reliability but are expensive and time-consuming both to the component supplier and the user.

As a result, complex components and subsystems for space usage have lagged those adopted for commercial use which largely do not follow the same Mil-Spec methods for establishing quality and demonstrating reliability. For microcontrollers, field programmable gate arrays (FPGAs), and systems on a chip (SOCs) for example, the space-approved components are two to three technology generations behind the current state-of-the art (SOTA) commercially available components. Market share analysis reported in multiple sources consistently shows that military and space components make up an ever-diminishing percentage of the market and are currently estimated to be 0.1% of the total component world market and 1% of the semiconductor market. It is imperative to use COTS to expand the components available to missions due to the shrinking Mil-Spec component market share and lagging capability.

For short development span programs (< 3 years ATP to launch), the emphasis will be on units that are already designed and are largely build-to-print or are already built and available in inventory. Using build-to-print units with COTS components doesn't fully address the changing landscape where we need to deliver higher performing systems under shorter development timelines that leverage commercial technologies, so developments using the SOTA components is vital<sup>1</sup>. It should be noted that while short development span programs may use COTS units, the buyer of the COTS units should ask the questions in Section 5.1 to fully understand if any unacceptable risk surfaces. The developers of the COTS units, when doing their developments, are encouraged to use this ATR to surface and be fully informed in their risk mitigation decisions.

This ATR endeavors to help address this conundrum by introducing and expanding on the concept that component selection is a broad trade space that must be factored into system design and test, and the mission's risk profile. Fundamentally, it is an incorrect assumption that all military or space-grade components (passives, discretes, actives, etc.) will show better reliability performance than COTS. Also, it is an incorrect assumption that a COTS component will always deliver better technical performance than a military or space-grade component in the required application. To paraphrase Thomas Jefferson, not all components are created equal. Under our definition of COTS lay a spectrum of components that range from unsuitable for many space applications to those that have demonstrated reliability and performance on par with or exceeding traditional military or space-grade components. By applying the guidelines laid out in this ATR and adhering to the component datasheet, a user will learn methods, best practices and mitigations that will help them better exploit the current landscape of components in their designs and enable future missions that will meet the needs under the changing landscape.

Components that can operate in the space environment are important to support US strategic interests. Flying components in space often requires many attributes, to include:

- Strict quality requirements

- Radiation effects knowledge for susceptible components

- Operation over large thermal swings

- Survival from shock and vibration

- Operation in vacuum

- Acoustic pressure

- EMC/EMI effects

- Long powered-on service life

- Component build knowledge

Many of these attributes are tied to the space environment which is difficult and unforgiving, including radiation, shock, vibration, and temperature extremes. This is exacerbated by the inability to maintain (replace) the vast majority of space hardware once on orbit. Currently, a great deal of effort is expended in component-level testing and verification that these needs are properly met. Because this assurance testing is time consuming and expensive, the components ultimately approved for satellite usage are behind the curve as compared with the current state of the art. As a result, the current baseline of space-grade components that meet the attributes above also have the following negative attributes including, lagging the industry state of the art, limited selection of qualified devices and uneven supply chain availability.

COTS spans an unbounded trade space of capabilities, performance levels, quality, inherent reliability, and environmental ranges. As such the burden is on the user to understand the limitations and promises of the datasheet combined with knowledge of the manufacturer to select components that meet mission requirements. COTS components can also provide some very tangible benefits to space programs. Besides the potential performance increase and shorter acquisition times, the components are much lower cost since appropriate components for selection are designed and manufactured for reliability, safety, capability, cost, and delivery time, unlike the premise of the Mil-Spec system, which has little consideration for anything outside of safety, quality, and reliability.

Modern manufacturing, technology, and statistical process controls today in many cases provide more robust COTS components to tolerate these challenging regimes, thus providing much greater performance and reliability, at lower cost. This has been particularly true for components designed and manufactured for the automotive and medical industries which have established controls and process qualification to achieve high quality (AEC-Q004, Automotive Zero Defects Framework) and demonstrated reliability for applications across diverse thermal, electrical, and mechanical environments that align with or encompass those seen for space applications<sup>3</sup>. The one clear difference is demonstrated radiation performance. However, a large majority of components used in space hardware designs do not exhibit radiation susceptibility and therefore it is not a consideration for those components (based on a survey of several space unit designs, a typical bill of materials for an electronic unit has > 75% passives and discretes that are not radiation susceptible). All complex components (FPGAs, SoC, multi-core processors, etc.) that do exhibit radiation susceptibility must be characterized as part of the component selection and design process, with particular emphasis on understanding SEE. Additional considerations need to be made for other potential knowledge gaps associated with COTS component packaging, internal build process and materials, and expected reliability if there is limited or no heritage performance to assess. These gaps need to be identified as early as possible as part of component selection by consulting the datasheet and supplier product information so that they can be addressed, and any risks mitigated, as part of the design trade space.

One feature of component selection that needs to be emphasized with COTS components, although it is true with all components, is that it is critical to identify the "right components from the right suppliers". As discussed above, certain types of industries levy controls but not all suppliers follow or fully implement those controls. Also broadly true is that it is critical to utilize all components within their datasheet limits with appropriate considerations for part selection and derating to meet required design and operational margins. For example, many military components such as capacitors are rated to Vr and designed to 2Vr (where Vr is the operational voltage) whereas many COTS capacitors are rated and designed to Vr. Therefore, to get the same design margin the user would need to select a part rated at 2Vr

for their application. For complex components, these considerations extend to many additional critical parameters besides voltage rating or current carrying capacity and cannot be ignored by the user. This discussion feeds into the broader fact that properly informed judgments about how to select components as part of the trade space are necessary, and the information to develop and support such judgments is provided in Sections 3, 4, and 5. Furthermore, in many cases, there will be no component available, COTS, military or space-grade, to meet all the necessary criteria, and thus mitigations will be needed in circuit, system design, and testing.

In some cases, no components will be available that satisfy all the necessary criteria combining resource and time constraints with long-term reliability in space, so several mitigations provided in Section 5 leverage the lower cost and shorter acquisition time to allow programs to assess the COTS insertion and development risk earlier. A typical design with Mil-Spec components goes through an engineering model (EM) to flight unit development period. Typically, the EM components are cheaper than their flight versions, using abbreviated test versions of the flight components (since the flight components have long *serial* testing as part of their schedule), but are still expensive relative to COTS. COTS components can be purchased early and more of them procured, which allows component risk reduction testing to be performed in parallel, leveraging an advantage of COTS. COTS components provide an opportunity to use alternate approaches (mitigations) with a wider array of components to realize a viable system leveraging component quality through high volume, automated manufacturing lines with strict statistical process control of a qualified process instead of low volume, semi-automated manufacturing lines with screening and lot-specific qualification.

## 2.1 Acquisition Considerations

It must be recognized that as the acquisition process proceeds, additional mitigations or the scope of known mitigations may change. For example, during the proposal phase, a mitigation to reset a component periodically may be identified as required due to SEE performance. As the design progresses (Section E of the flow, Figure 6) it may become necessary to change the system timing and Flight Software (FSW) to fully incorporate the desired reset function. The overall architecture needs to be considered as an integral part of the system solution. For new non Mil-Spec or non-RHA (Radiation Hardness Assurance) components, the system acquisition process may be as long as the Mil-Spec process with its known qualities (highly dependent on program schedule and cost constraints, component chosen and potential mitigations). While the usage of COTS components and units, if selected wisely, promises gains in performance and cost, that gain comes with some loss of knowledge about the component. There is an implicit trade between the COTS component and its required mitigations (if any) vs the cost and schedule of the Mil-Spec component. There needs to be a recognition that the acquisition process needs to change to use COTS components and units for program spectrum that span three years from ATP to launch to the long duration class A national asset type. The acquisition strategy for the range of programs that incorporate COTS components is documented in Acquisition Considerations to Expand Space Design Options using COTS Electrical, Electronic, and Mechanical (EEE) Parts and Units (ATR-2023-01981).

It is up to programs to decide what best practices, questions, and mitigations are consistent with their program constraints. It should also be recognized that a COTS component "qualified" for a particular application may not be equivalent to qualification of a Mil-Spec component as the COTS component "qualification" may be application dependent.

The holistic approach dictates that changes to space system architectures also may need to be revised when considering the use of COTS components. The following lists several changes that should be considered.

- a) Redundancy: To increase the reliability of the system, designers would need to incorporate redundancy in the design of the constellation architecture. This could include using multiple spacecraft in each orbital plane or using multiple orbital planes. This would be of consideration when one is confined to using COTS that are not established as reliable or that are used outside of their datasheet limits.

- b) Fault-tolerance: The architecture would need to be designed to be more fault-tolerant, so that it can continue to function even if one or more functions fail. This could involve using redundant items or designing the architecture to automatically switch to a backup mode in the event of a failure. This would be of consideration when one is confined to using COTS that are not established as reliable or that are used outside of their datasheet limits.

- c) Scalability: The architecture should be scalable, so that new spacecraft or subsystems can be easily added or removed as needed or as increased performance technology becomes available. This would allow for the system to be expanded or contracted as required.

- d) Distributed architectures: The constellation could be designed in a distributed architecture, where each spacecraft is able to operate independently, and the system can continue to function even if one or more spacecraft fails.

- e) Continuous monitoring: The architecture and systems should include a continuous monitoring function that would allow the system to detect any signs of degradation or failure in the select EEE components (first time use). This would be of consideration when one is confined to using components that are not established as reliable or that are used outside of their datasheet limits where the program risk profile cannot accommodate TD or SEE testing.

- f) Changes to satellite designs may also be considered. Satellite integrators should consider designing their system in a modular, scalable fashion. Satellites should be designed to allow plug and play architectures such that different configurations of satellite box elements can be combined depending on mission requirements.

Satellite unit providers (such as Star Trackers, Reaction Wheels, etc.) should produce modular scalable performance boxes in a somewhat continuous fashion. Standard off the shelf units could be redesigned on a planned periodic basis to roll technology improvements into new generations of units.

For long term constellations, a Diminishing Manufacturing Sources and Material Shortages (DMSMS) program will need to be established as COTS EEE components often have relatively short life cycles compared to military and space EEE parts. A good DMSMS program requires periodic re-design to replace or improve functions, not just EEE components. Strategic characterization of COTS parts technologies that factors in how certain component types evolve with technology, supply chain evolution, or material availability can strongly contribute to such a program.

## 3. Informed Risk Flow

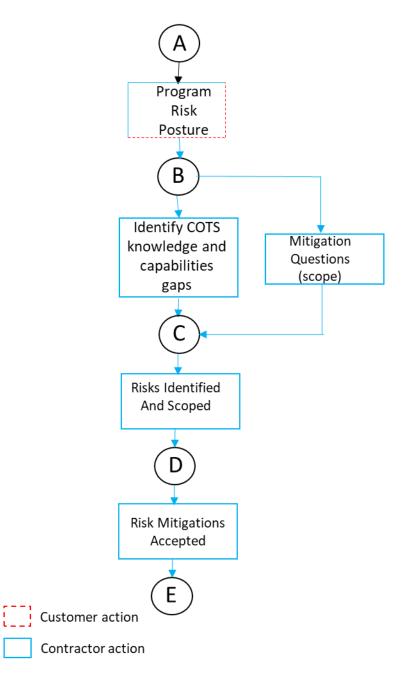

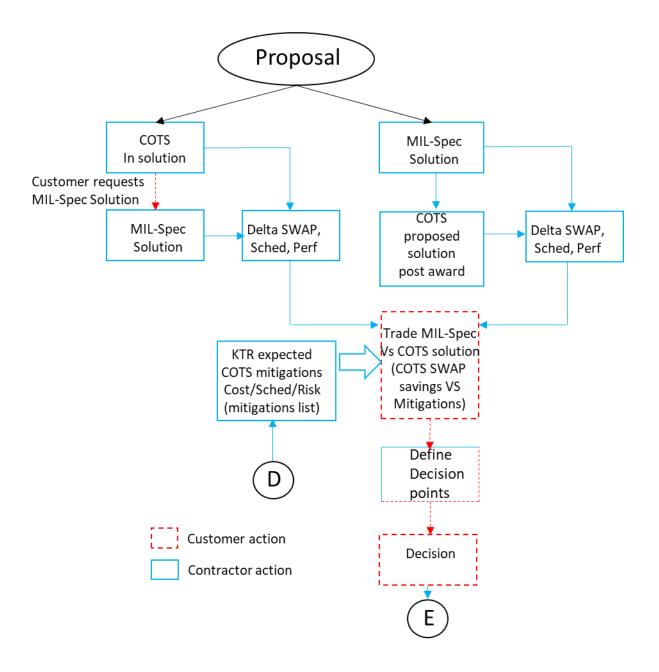

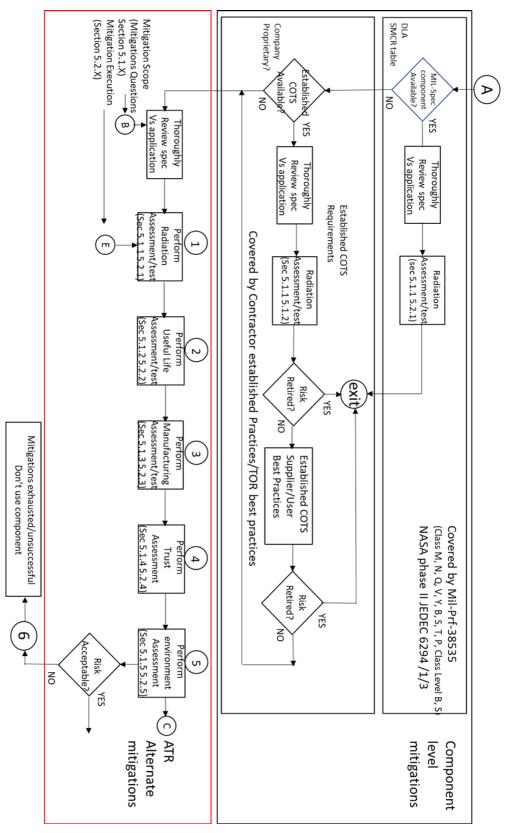

The key word in this process is "informed". The flowcharts in this section are intended to provide guidance to understand and define the insertion and development risk the program is willing to tolerate when considering COTS components in the design solution. The flow is laid out to first determine what the insertion risk level for the program will be. This is intended to be a joint customer and contractor conversation. Figure 1 shows the overarching informed risk flow. Figures 2-5 provide the detailed steps and decision points embedded in the informed risk flow that culminate in execution of the accepted design solution by the program.

The informed risk flow in Figure 1 is broken up into nodes, identified as A-E, with each node representing a waypoint that needs to be reached prior to moving on to the next phase of the flow. Node A represents the start or inception of the program or associated effort. This could be as early as a pre-Request for Proposal (RFP) phase or as part of the Authorization to Proceed (ATP) for the effort. Node B represents achieving a definitized program risk posture regarding usage of COTs to achieve necessary cost, schedule, and technical performance requirements. Node C represents determination of the potential risk mitigations that can be applied to meet the program risk posture. Node D represents arriving at a scoped risk mitigation plan that incorporates all relevant best practices for addressing a candidate COTs design. Node E represents transition to program execution of the accepted solution which may be COTs, MIL-Spec or a combined design, and then implementation of the design and associated features.

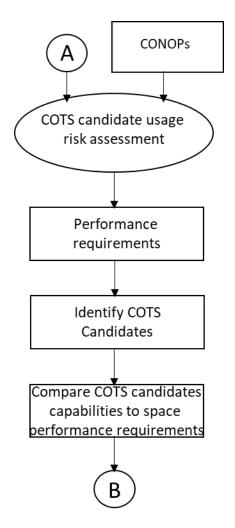

The intention of this ATR is to provide information for any mission class so that the program may determine the best course of action for their COTS insertion risk tolerance, including potential risk mitigations, after deciding the insertion and development risk posture for the program. Once the risk posture has been jointly decided, the assessment of any COTS components as part of the proposal can be done. Figure 2 (nodes A to B) shows the actions to determine the program COTS insertion risk tolerance and if needed, cost and schedule decision points. It also illustrates that the CONOPs for the mission should be incorporated as part of the initial assessment effort.

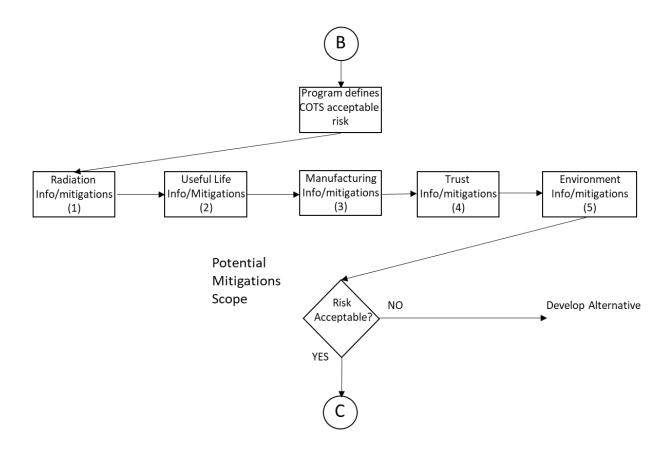

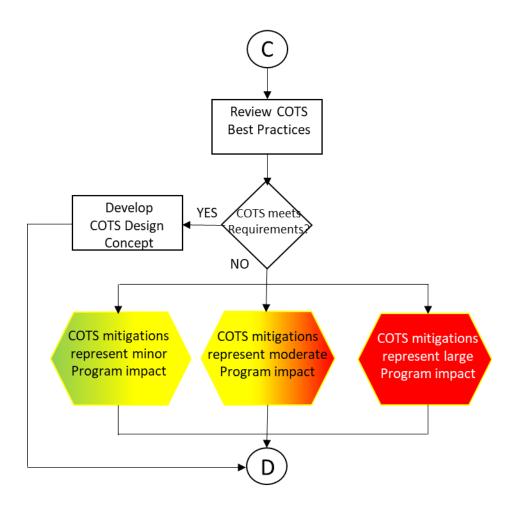

Figure 3 (nodes B to C) shows the actions to be taken to assess the COTS component insertion and development risk. It is intended that the risk assessment questions in Section 5.1 (mitigation questions) are considered during this part of the flow as well as the commensurate mitigations to determine the mitigation scope early. The questions in Section 5.1 correspond to the detailed mitigation flows for easy correlation. Once the component insertion risk and mitigation scope has been determined, it is recommended that the best practices list be considered as they may alleviate some of the mitigation scope. Figure 4 (nodes C to D) shows the informed risk determination after consulting the best practices list found in Section 4 of this ATR. The best practices are broken into two main sections: the desired supplier best practices (4.1) and the user best practices (4.2).

The desired supplier best practices are based on the best practices of suppliers when providing Mil-Spec components. It is not expected that COTS component suppliers will provide the best practice information found in Table 1. Since it is expected that some of the information in Table 1 will not be available, the best practices list by the user was developed to augment the lack of information from the supplier. These suggested user best practices were compiled to avoid employing the mitigations found in Section 5. Table 2 shows general user best practices for components. Table 3 through Table 18 are user best practices by components for quick reference.

For the informed Risk Flow in Figure 5 (nodes D to E), the left side of the flow is for the occasion where the usage of COTS is known during the proposal phase. The right side is the proposal to use COTS components that occurs after the proposal and uses the same data to assess the COTS insertion risk. Exiting point E is the start of program execution. This represents the second pass through Section 5.2 to execute the selected mitigations. The flow in Figure 6 is essentially in parallel with the informed risk flow from flow Sections B to D for searching the Standard Military Cross Reference Matrix (SMCR) as an aid before concluding only a COTS component can meet the requirement, the questions, and scope, while the mitigation details are employed at flow Section E. It is recognized that for a short duration, short procurement mission that the usage of some Mil-Spec components or units may not be feasible due to their procurement lead time and that some of the steps outlined below may be skipped (for example, developing and trading off a Mil-Spec solution). The essence of COTS usage is a multivariable trade of cost, schedule, weight, and power of the Mil-Spec component solution vs the unknowns of the COTS solution (which promises substantial performance and SWAP advantage with potential mitigation impacts). Being informed about the advantages and disadvantages of both is the key to a good decision for the program.

Figure 1. Informed risk flow (A to E).

Figure 2. Informed risk flow – Determine COTS risk tolerance (A to B).

Figure 3. Informed risk flow – COTS mitigation scope (B to C).

Figure 4. Informed risk flow – Scoping risk mitigation (C to D).

Figure 5. Informed risk flow – Selecting the design solution (D to E).

## 4. Best Practices

The best practices are broken into two groups, general best practices for COTS components and COTS best practices by component.

The general best practices are broken down to best practices by the supplier and by the component user. It is desired that the supplier performs the best practices found in Table 1, to choose a component from a supplier with known quality. Refer to NESC-RP-19-01490 Recommendations on Use of COTS Guidance for NASA Missions Phase II (11-10-22 NRB) RP FINAL Section 7.1.3.1 for the definitions of the terminology and success criteria.<sup>2</sup> If the suppler does not perform these best practices or is unwilling to supply supporting information of their process, it may be necessary for the component user to use some of the best practices found later in Section 4.1 and perform some of the mitigations in Section 5.

Table 1. Supplier Best Practices

Best Practices for COTS Components (Supplier) Process stability for at least one year<sup>2</sup> Product produced in high volume<sup>2</sup> 100% electrical test<sup>2</sup> Multi-lot charaterization<sup>2</sup> Fully automated line<sup>2</sup> Undergoes in-process testing<sup>2</sup> Maintains consistent yield<sup>2</sup>

#### 4.1 General COTS best Practices

The general best practices for COTS components, shown in Table 2, are generic and may also apply to Mil-Spec components, but were compiled to apply to COTS components. These best practices are from the MSIW (Mission Success Information Workshop) sub-team for COTS best practices and is intended to be considered when developing the program informed risk flow (Section C).

| Number | Best Practices for COTS component (user)                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | For a given COTS, once the program has defined the necessary best practices and                                                                                                                                                                                                                                                                                                                                                                               |

|        | mitigations, develop a plan to deal with the higher cost and schedule risk items first <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                           |

| 2      | Consider not having the COTS in a critical timing/ mission path (although it is                                                                                                                                                                                                                                                                                                                                                                               |

|        | recognized that COTS is likely a part of the critical path for performance reasons) <sup>2, 5, 12, 16</sup>                                                                                                                                                                                                                                                                                                                                                   |

| 3      | Consider the fault management implications (fault/degradation mechanisms) <sup>4, 5, 12, 16, 23</sup>                                                                                                                                                                                                                                                                                                                                                         |

| 4      | Consider on orbit monitoring of key performance parameters for trending COTS performance particularly for supplier non tested parameters) <sup>12</sup>                                                                                                                                                                                                                                                                                                       |

| 5      | Conduct COTS component level FMEA (not functional level) to understand the systems effects of the COTS faults and potential propagation effects <sup>2, 4, 5, 12,16, 23</sup>                                                                                                                                                                                                                                                                                 |

| 6      | Consider the component failure rate and number of times used for critical applications as an element of the program risk assessment <sup>16</sup>                                                                                                                                                                                                                                                                                                             |

| 7      | Upon failure of a COTS component, the program/project should initiate a failure analysis, and all efforts within available resources should be made to determine root cause. The first steps to root cause determination should be to verify that the component's datasheet was not violated in processing, testing, or usage <sup>2</sup>                                                                                                                    |

| 8      | Pay particular attention to COTS absolute and recommended ratings (different from Mil-Spec components). Scrutinize the datasheet carefully <sup>4, 16, 20</sup>                                                                                                                                                                                                                                                                                               |

| 9      | Bring in senior peer reviewers early to consider the impacts of the COTS(s) in the design/board/unit/system <sup>12, 16, 23</sup>                                                                                                                                                                                                                                                                                                                             |

| 10     | Consider large design margins for poorly analyzed/tested COTS parameters - verify through test <sup>2, 8, 9, 16, 23</sup>                                                                                                                                                                                                                                                                                                                                     |

| 11     | Reserve extra connector pins for test points early with the expectation that a key parameter will need to be monitored at unit level (particularly for COTS with no burn-in testing) <sup>4, 12</sup>                                                                                                                                                                                                                                                         |

| 12     | Consider standard interfaces over proprietary/unique interfaces <sup>23</sup>                                                                                                                                                                                                                                                                                                                                                                                 |

| 13     | Consider the obsolescence aspect of the component chosen. Obsolete in a year may mean no supplier support at the end of the program <sup>2, 3, 5, 16</sup>                                                                                                                                                                                                                                                                                                    |

| 14     | Make as much usage as possible of supplier toolkits, simulation models, and development aids. Perform a careful review of the development tool parameters vs the FLT parameters (for example, a processor development kit may run full clock speed and use faster memory than the flight application, so the FLT processor throughput will be less than that of the development kit (the code may run faster on the development kit) <sup>2, 10, 16, 23</sup> |

| 15     | For interface components, VERIFY that the components are truly capable of cold<br>sparing and do not act as a sneak path (example, Honeywell HX422R and HX422D<br>are NOT cold spare capable, so cannot be used for a cross strap application with a<br>powered component connected. Many commercial components do not need to<br>operate in a cross strap (redundancy) configuration                                                                         |

| 16     | Reserve a greater than standard SWAP reserve for the assemblies with COTSs to absorb the mitigation impacts <sup>3, 4, 23</sup>                                                                                                                                                                                                                                                                                                                               |